728x90

- the instruction class add consists of four addition instructions: addb, addw, addl, and addq, adding bytes, words, double words, and quad words, respectively

3.5.1 Load Effective Address

- The load effective address instruction leaq is actually a variant of the movq in- struction. It has the form of an instruction that reads from memory to a register, but it does not reference memory at all.

3.5.2 Unary and Binary Operations

- Operations in the second group are unary operations, with the single operand serving as both source and destination. This operand can be either a register or a memory location

- when the second operand is a memory location, the processor must read the value from memory, perform the operation, and then write the result back to memory.

3.5.3 Shift Operations

- when register %cl has hexadecimal value 0xFF, then instruction salb would shift by 7, while salw would shift by 15, sall would shift by 31, and salq would shift by 63.

- there are two names for the left shift instruction: sal and shl. Both have the same effect, filling from the right with zeros. The right shift instructions differ in that sar performs an arithmetic shift (fill with copies of the sign bit), whereas shr performs a logical shift (fill with zeros).

3.5.4 Discussion

- Arguments x, y, and z are initially stored in registers %rdi, %rsi, and %rdx, respectively

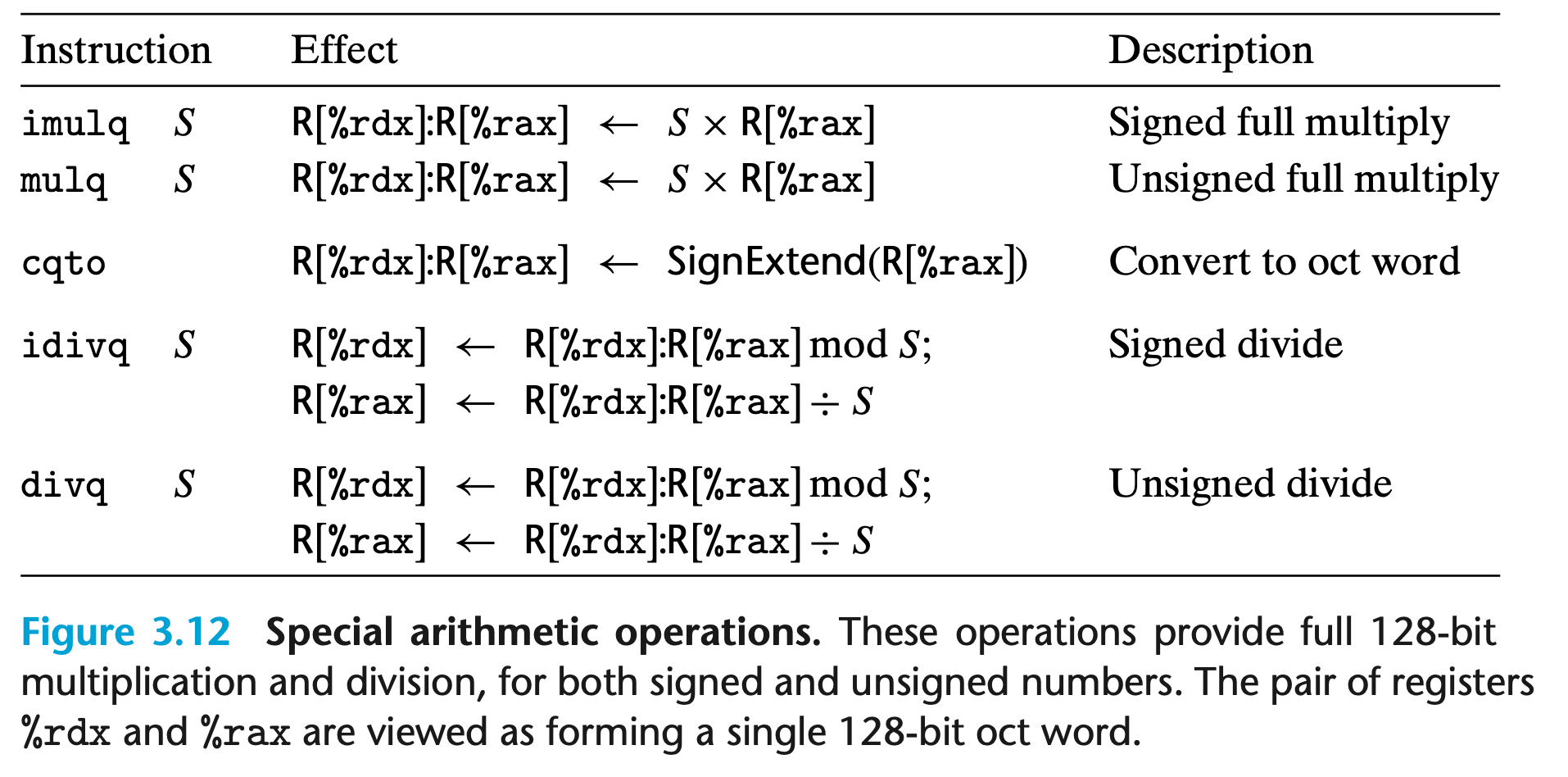

3.5.5 Special Arithmetic Operations

728x90

'csapp' 카테고리의 다른 글

| 3.6.5 Implementing Conditional Branches with Conditional Control (0) | 2023.04.13 |

|---|---|

| 3.6 Control (0) | 2023.04.10 |

| 3.4.2 Data Movement Instructions (0) | 2023.04.08 |

| 3.2.3 Notes on Formatting (0) | 2023.04.07 |

| 3 Machine-Level Representation of Programs (0) | 2023.04.06 |

댓글